High Bandwidth Memory (HBM) este o interfata a memoriei de computer de mare viteza pentru memorie sincrona cu acces aleator dinamic (SDRAM), stivuita 3D, produsa initial de Samsung, AMD si SK Hynix. Este utilizata impreuna cu acceleratoare grafice de inalta performanta, dispozitive de retea, centre de date de inalta performanta AI ASIC si FPGA si in unele supercomputere (cum ar fi NEC SX-Aurora TSUBASA si Fujitsu A64FX).

Primul cip de memorie HBM a fost produs de SK Hynix in 2013, iar primele dispozitive care au folosit HBM au fost GPU-urile AMD Fiji in 2015.

Memoria cu latime de banda mare a fost adoptata de JEDEC ca standard industrial in Octombrie 2013. A doua generatie, HBM2, a fost acceptata de JEDEC in Ianuarie 2016.

Tehnologie

HBM obtine o latime de banda mai mare in timp ce foloseste mai putina energie intr-un factor de forma substantial mai mic decat DDR4 sau GDDR5. Acest lucru se realizeaza stivuind pana la opt matrite DRAM si o matrita de baza optionala care poate include circuite tampon si logica de testare. Stiva este adesea conectata la controlerul de memorie de pe un GPU sau CPU printr-un substrat, cum ar fi un interposer de siliciu.

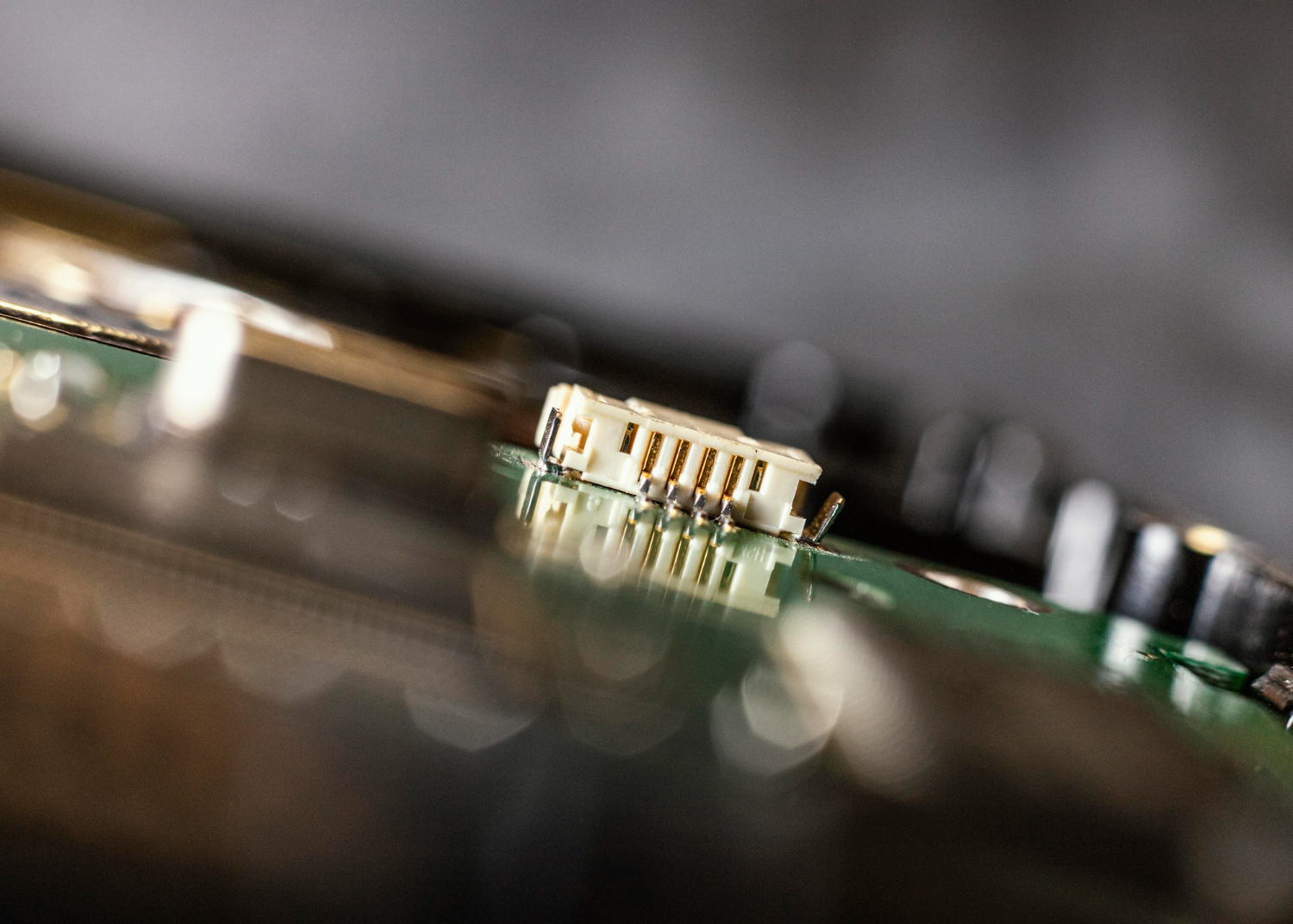

Alternativ, memoria ar putea fi stivuita direct pe cipul CPU sau GPU. In cadrul stivei, matritele sunt interconectate vertical prin via-siliciu (TSV) si microbumps. Tehnologia HBM este similara in principiu, dar incompatibila cu interfata Hybrid Memory Cube (HMC) dezvoltata de Micron Technology.

Magistrala de memorie HBM este foarte larga in comparatie cu alte memorii DRAM precum DDR4 sau GDDR5. O stiva HBM de patru matrite DRAM (4-Hi) are doua canale de 128 biti per matrita pentru un total de 8 canale si o latime de 1024 biti in total. O placa grafica / GPU cu patru stive HBM 4-Hi ar avea, prin urmare, o magistrala de memorie cu o latime de 4096 biti. In comparatie, latimea magistralei de memorii GDDR este de 32 de biti, cu 16 canale pentru o placa grafica cu o interfata de memorie de 512 biti. HBM accepta pana la 4 GB per pachet.

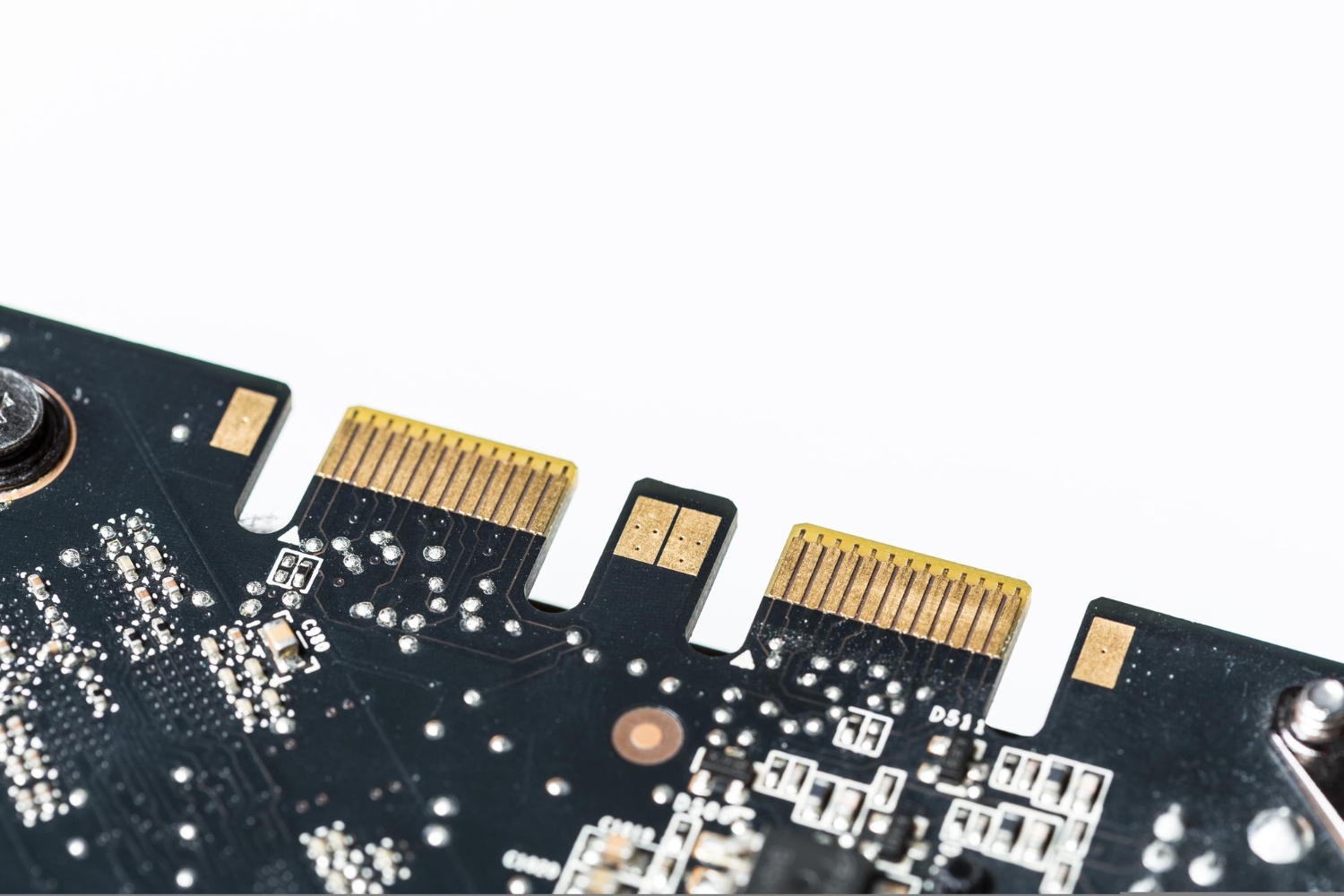

Numarul mai mare de conexiuni la memorie, in raport cu DDR4 sau GDDR5, a necesitat o noua metoda de conectare a memoriei HBM la GPU (sau alt procesor). AMD si Nvidia au folosit ambele cipuri de siliciu construite special, numite interpozitori, pentru a conecta memoria si GPU-ul. Acest interpozitor are avantajul suplimentar de a cere ca memoria si procesorul sa fie apropiate fizic, scazand lungimea cailor de memorie.

Cu toate acestea, deoarece fabricarea dispozitivelor semiconductoare este semnificativ mai scumpa decat fabricarea placilor cu circuite imprimate, acest lucru se adauga la costul produsului final.

Interfata

HBM DRAM este strans cuplat la matrita de calcul gazda cu o interfata distribuita. Interfata este impartita in canale independente. Canalele sunt complet independente unele de altele si nu sunt neaparat sincronizate intre ele. HBM DRAM utilizeaza o arhitectura cu interfata larga pentru a obtine o functionare de mare viteza, cu putere redusa. HBM DRAM foloseste un ceas diferential de 500 MHz CK_t / CK_c (unde sufixul „_t” reprezinta componenta „adevarata” sau „pozitiva” a perechii diferentiale, iar „_c” reprezinta partea „complementara”). Comenzile sunt inregistrate la varful ascendent al CK_t, CK_c. Fiecare interfata de canal mentine o magistrala de date pe 128 de biti care functioneaza la o rata de date dubla (DDR). HBM accepta rate de transfer de 1 GT / s per pin (transfer de 1 bit), obtinand o latime de banda totala a pachetului de 128 GB / s.

HBM2

A doua generatie de memorie cu latime de banda mare, HBM2, specifica, de asemenea, pana la opt matrite pe stiva si dubleaza ratele de transfer ale pinilor de pana la 2 GT / s. Pastrand accesul de 1024 biti, HBM2 poate atinge o latime de banda de memorie de 256 GB / s per pachet. Specificatia HBM2 permite pana la 8 GB per pachet. Se prevede ca HBM2 va fi util in special pentru aplicatiile de consum sensibile la performanta, cum ar fi realitatea virtuala.

La 19 Ianuarie 2016, Samsung a anuntat productia de masa timpurie a HBM2, pana la 8 GB pe stiva. SK Hynix a anuntat, de asemenea, disponibilitatea stack-urilor de 4 GB in August 2016.

HBM2E

La sfarsitul anului 2018, JEDEC a anuntat o actualizare a specificatiei HBM2, oferind latime de banda si capacitati crescute. Viteza de pana la 307 GB / s pe stiva (rata efectiva de date de 2,5 Tbit / s) este acum acceptata in specificatiile oficiale, desi produsele care functioneaza la aceasta viteza erau deja disponibile. In plus, actualizarea a adaugat suport pentru stive 12-Hi (12 matrite), facand posibile capacitati de pana la 24 GB per stiva.

La 20 Martie 2019, Samsung si-a anuntat Flashbolt HBM2E, cu opt matrite pe stiva, o rata de transfer de 3,2 GT / s, oferind un total de 16 GB si 410 GB / s pe stiva.

12 August 2019, SK Hynix a anuntat HBM2E, cu opt matrite pe stiva, o rata de transfer de 3,6 GT / s, oferind un total de 16 GB si 460 GB / s pe stiva iar La 2 Iulie 2020, aceeasi companie a anuntat ca a inceput productia in serie.

HBM3

La sfarsitul anului 2020, Micron a dezvaluit ca standardul HBM2E va fi actualizat si, alaturi de acesta, au dezvaluit urmatorul standard cunoscut sub numele de HBMnext (redenumit ulterior HBM3). Acesta este un mare salt generational de la HBM2. Acest nou VRAM va veni pe piata in trimestrul IV al anului 2022. Acest lucru va introduce probabil o noua arhitectura, asa cum sugereaza denumirea.

In timp ce arhitectura ar putea fi revizuita, scurgerile de informatii indica o performanta similara cu cea a standardului HBM2E actualizat. Este probabil ca aceasta memorie RAM sa fie utilizata mai ales in GPU-urile centrelor de date.

La mijlocul anului 2021, SK Hynix a dezvaluit cateva specificatii ale standardului HBM3, cu viteze I / O de 5,2 Gbit / s si latime de banda de 665 GB / s pe pachet.

HBM-PIM

In Februarie 2021, Samsung a anuntat dezvoltarea HBM cu procesare in memorie. Aceasta noua memorie aduce capacitati de calcul AI in interiorul memoriei, pentru a creste prelucrarea pe scara larga a datelor. Un motor AI optimizat DRAM este plasat in fiecare banc de memorie pentru a permite procesarea paralela si pentru a minimiza miscarea datelor. Samsung sustine ca acest lucru va oferi o performanta dubla a sistemului si va reduce consumul de energie cu peste 70%, fara a necesita modificari hardware sau software pentru restul sistemului.

Background

Memoria stivuita a fost comercializata initial in industria memoriei flash. Toshiba a introdus un cip de memorie flash NAND cu opt matrite stivuite in Aprilie 2007, urmat de Hynix Semiconductor introducand un chip flash NAND cu 24 de matrite stivuite in Septembrie 2007.

Memoria 3D cu acces aleatoriu (RAM) utilizand tehnologia through-silicon via (TSV) a fost comercializata de Elpida Memory, care a dezvoltat primul cip DRAM de 8 GB (stivuit cu patru matrite DDR3 SDRAM) si l-a lansat in Iunie 2011. Tot in 2011, SK Hynix a introdus memorie DDR3 de 16 GB (clasa de 40 nm) folosind tehnologia TSV, iar Samsung Electronics a introdus 32 GB DDR3 de 32 GB (clasa de 30 nm) bazata pe TSV in Septembrie.

JEDEC a lansat pentru prima data standardul JESD229 pentru memorie IO de banda larga, acesta fiind predecesorul HBM, cu patru canale de 128 biti, in Decembrie 2011, dupa cativa ani de munca. Primul standard HBM JESD235 a urmat in Octombrie 2013.

Dezvoltare

Dezvoltarea memoriei cu latime de banda mare a inceput la AMD in 2008 pentru a rezolva problema cresterii consumului de energie si factorului de forma al memoriei computerului. In urmatorii cativa ani, AMD a dezvoltat proceduri pentru rezolvarea problemelor de stivuire cu o echipa condusa de Bryan Black. Pentru a ajuta AMD sa-si realizeze viziunea HBM, compania a apelat la parteneri din industria memoriei, in special la compania coreeana SK Hynix, care a avut o experienta anterioara cu memoria stivuita 3D, precum si parteneri din industria interpozitorilor (compania taiwaneza UMC).

Dezvoltarea HBM a fost finalizata in 2013, cand SK Hynix a construit primul cip de memorie HBM. HBM a fost adoptat ca standard industrial JESD235 de JEDEC in Octombrie 2013, in urma unei propuneri a AMD si SK Hynix din 2010. Productia de volum mare a inceput la o instalatie Hynix din Icheon, Coreea de Sud, in 2015.

Primul GPU care utilizeaza HBM a fost AMD Fiji, lansat in Iunie 2015, implementat pe AMD Radeon R9 Fury X.

In Ianuarie 2016, Samsung Electronics a inceput productia de masa a HBM2. In aceeasi luna, HBM2 a fost acceptat de JEDEC ca standard JESD235a. Primul cip GPU care utilizeaza HBM2 este Nvidia Tesla P100, care a fost anuntat oficial in Aprilie 2016.

Viitor

La conferinta Hot Chips din August 2016, atat Samsung, cat si Hynix au anuntat tehnologiile de memorie HBM de urmatoarea generatie. Ambele companii au anuntat produse de inalta performanta ce vor avea densitate crescuta, latime de banda crescuta si consum redus de energie. Samsung a anuntat, de asemenea, o versiune cu costuri mai mici a HBM care se afla in curs de dezvoltare si care vizeaza pietele de masa. Indepartarea matritei tampon si scaderea numarului de TSV-uri scade costul, desi in detrimentul unei latimi de banda generale scazute (200 GB / s).